为证券之星据公开信息整理,由智能算法生成,不构成投资建议。

为证券之星据公开信息整理,由智能算法生成,不构成投资建议。

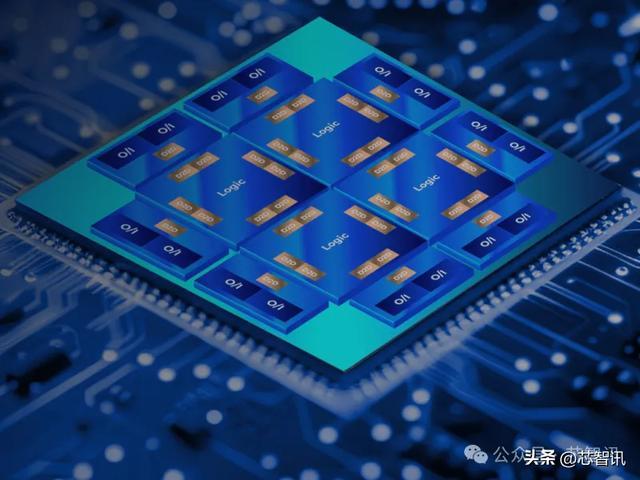

12月23日消息,加拿大半导体IP公司Alphawave Semi 近日展示了业界首个用于通用小芯片互连 (Universal Chiplet Interconnect Express,UCIe) 技术的 64 Gbit/s Die-to-Die (D2D) IP 子系统。

据介绍,该第三代小芯片互联 IP 将采用台积电3nm制程 工艺构建,并基于台积电的先进封装技术和标准,遵循最新的 Gen2 36 Gbit/s 和 Gen1 24 Gbit/s 实现,同样也采用台积电 3nm 制程工艺。该级别的互连带宽可实现超过 20 Tbit/s/mm 的带宽密度,并且具有低功耗和低延迟优势。该 IP 具有高度可配置性,支持多种协议,包括 AXI-4、AXI-S、CXS、CHI 和 CHI-C2C,以满足高性能计算 (HPC)、数据中心和人工智能 (AI) 应用中对分解系统对高性能连接日益增长的需求。

该设计符合最新的 UCIe 规范,并具有可扩展的架构,具有高级可测试性功能,包括实时每通道健康监控。

UCIe D2D 互连有助于实现一系列标准和新兴的小芯片连接场景。常见用途包括通过 UCIe 的流功能链接计算小芯片以实现低延迟、一致的连接,以及使用带有 PCIe、CXL 或以太网的 UCIe 接口将计算连接到 I/O 小芯片。

光重定时器可用于通过光引擎建立可靠、低延迟的光 I/O 链路,从而增强系统外连接。这支持了数据中心和 AI/ML 系统中低功耗、高速解决方案的开发。

对于高性能应用,使用最新的 UCIe 标准来自创建自定义 HBM 基础芯片是一种尖端方法,它涉及将内存芯片与计算芯片紧密集成,以实现极高的带宽以及组件之间的低延迟。这允许重复使用主芯粒上已经占用的芯粒到芯粒接口,用于内核到内核、或内核到 I/O 连接。这种方法极大地优化了 AI 应用程序中的内存事务。

“UCIe 联盟很高兴看到成员实现流片等关键里程碑,这表明 UCIe 规范的采用率越来越高,”UCIe 联盟营销工作组主席 Brian Rea 说。“UCIe 是小芯片行业的基石,为高速、低延迟的 die-to-die 互连提供了强大的解决方案。通过采用开放标准,我们使行业能够加速创新、缩短上市时间并提供突破性技术。

“我们在3nm技术上以36 Gbit/s的速度成功实现了Gen2 UCIe IP的流片,这建立在我们开创性的经过硅验证3nm UCIe IP与CoWoS封装的基础之上,”Alphawave Semi高级副总裁兼总经理Mohit Gupta说。这为我们的 64 Gbit/s 的 Gen3 UCIe IP 奠定了基础,目标是在 2025 年为需要最大化海岸线密度以满足关键 AI 带宽需求的客户提供高性能、20 Tbit/s/mm 的吞吐量功能。

编辑:芯智讯-林子白银配资线上